Opis

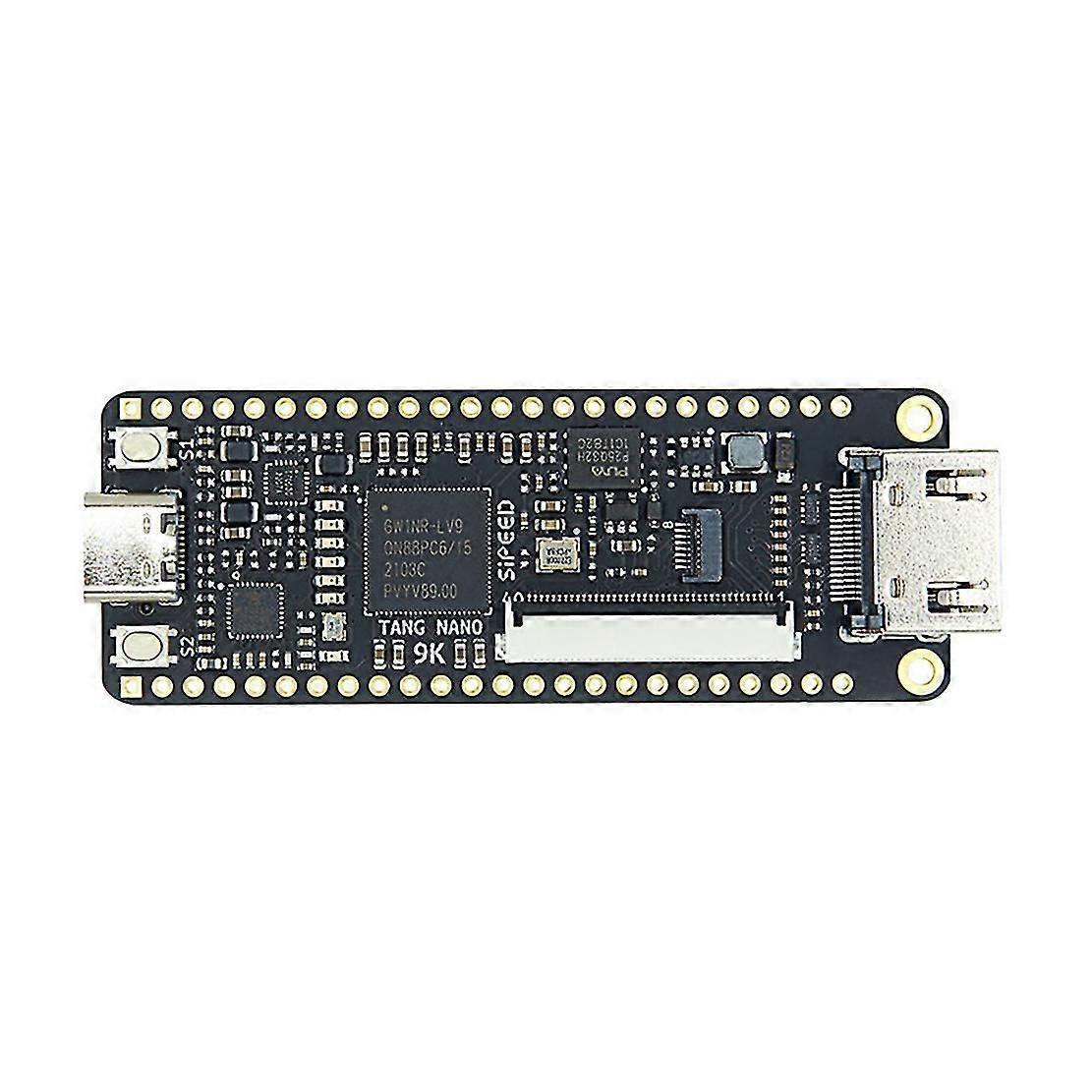

1, dla Tang Nano 9K to kompaktowa płytka rozwojowa oparta na układzie FPGA Gowin GW1NR-9.

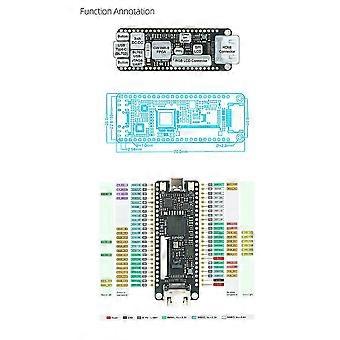

2, Jest kompatybilne ze złączem, złączem ekranu interfejsu RGB, złączem ekranu SPI, SPI FLASH i 6 pozwalają użytkownikom łatwo i szybko przeprowadzić weryfikację FPGA, weryfikację miękkiego rdzenia RISC-V i weryfikację funkcjonalnego prototypu.

3, jednostka logiczna 8640 LUT4 należąca do GW1NR-9 może być nie tylko używana do projektowania złożonych obwodów logicznych, ale może również uruchamiać kompletny miękki rdzeń PicoRV, który spełnia potrzeby użytkowników w zakresie nauki FPGA, weryfikacji miękkiego rdzenia i dogłębnego projektowania.

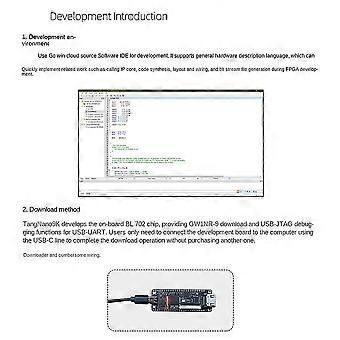

4. Dla Tang Nano 9K jest opracowywany przy użyciu oprogramowania Gowin Yunyuan IDE. Obsługuje ogólny język opisu sprzętu i może szybko realizować powiązane prace, takie jak wywoływanie rdzenia IP, synteza kodu, umieszczanie i routing oraz generowanie plików strumienia bitów w procesie tworzenia układów FPGA.

5. Wbudowany układ BL702 dla płytki rozwojowej Tang Nano9K zapewnia pobieranie USB-JTAG i funkcje debugowania USB-UART dla GW1NR-9. Użytkownicy muszą tylko użyć USB-C, aby podłączyć płytkę rozwojową do komputera, aby zakończyć operację pobierania, bez konieczności zakupu dodatkowego narzędzia do pobierania i kłopotliwego okablowania.

Konfiguracja rdzenia:

Jednostki logiczne (LUT4): 8640

Rejestr (FF): 6480

Rozproszona statyczna pamięć o dostępie swobodnym SSRAM (bity): 17280

Blokowa statyczna pamięć o dostępie swobodnym B-(bity): 468K

Liczba blokowych statycznych pamięci o dostępie swobodnym BSRAM (szt.): 26

Pamięć flash użytkownika (bity): 608K

PSRAM (bity): 64M

Wysokowydajny moduł DSP: obsługuje mnożenie 9X9, 18X18, 36X36bit i akumulator 54-bitowy

Mnożnik (mnożnik 18x18): 20

SPI FLASH: 32 m-bity

Elastyczne zasoby PLL: 2 Phase Locked (PLL)

Interfejs ekranu wyświetlacza: interfejs kompatybilny, interfejs ekranu SPI i interfejs ekranu RGB

Debugger: Wbudowany BL702 p, zapewniający pobieranie USB-JTAG i funkcje drukowania przez port szeregowy USB-UART dla GW1NR-9

IO: Obsługa 4mA, 8mA, 16mA, 24mA i innych możliwości napędu; zapewnia Bus Keeper, rezystory pull-up/pull-down i wyjście Open Drain dla każdego I/O

Złącze: uchwyt na kartę TF, podkładka nagłówka pinowego 2 * 24P 2,54 mm

: 2 programowalne przez użytkownika

: 6 programowalnych na pokładzie.

Materiał: PCB

Kolor:

Zawartość Paczki:

1 x płytka rozwojowa FPGA Tang Nano 9K

2 x złącze 2,54 pin

1 x do transmisji danych

Tylko powyższa zawartość opakowania, inne produkty nie są uwzględnione.

Uwaga: Światło i różne wyświetlacze mogą powodować, że kolor przedmiotu na zdjęciu będzie nieco różnił się od rzeczywistego. Dopuszczalny błąd pomiaru wynosi +/- 1-3 cm.

-

Identyfikator Fruugo:

400185262-851656739

-

EAN:

6195082403529